The need for secure electronic devices is pervasive at all levels; from banking transactions to defence and surveillance applications. Recent reports of the USA suspecting Chinese chip manufacturer of spying or commercial US chips having deep security bugs, brings to the fore the importance of self-reliance in technology to develop such electronic devices. In one such effort, Prof. Udayan Ganguly and his group from the Indian Institute of Technology Bombay (IIT Bombay) have developed a hardware-based encryption system to safeguard storage of data and e-commerce and banking transactions. Their innovation has been awarded the PK Patwardhan Technology Development Award by IIT Bombay.

The award, instituted in 2001, recognises the best technology developed by a team from IIT Bombay. The award is given in the memory of Dr. P.K. Patwardhan, the legendary solid state electronics engineer from BARC, who pushed the national electronics self-reliance policy and indigenous technology development in 1970s. "Indian engineers strongly contribute to innovation in electronics world-wide. To be recognized for our innovative technology development for India, in India, by India (i.e. jointly by IIT Bombay and SCL teams) is humbling and encouraging at the same time.” says Prof. Udayan Ganguly.

Prof. Udayan Ganguly’s research group is driving self-reliance in electronics by partnering with Indian Space Research Organisation’s Semiconductor Lab (SCL) at Chandigarh. After developing a bipolar junction transistor---a fast switch that is fundamental to electronic circuits---in collaboration with SCL, both have partnered again to develop indigenous technology for hardware-based encryption of electronics chips.

National Security is a key focus for nanoelectronics at IIT Bombay” notes Prof. Swaroop Ganguly, a team member, who leads the Nanoelectronics Network for Research and Applications (NNetRA) centre at IIT Bombay.

Encryption is a process of encoding information in a way where only authorised parties can access it. With software-based encryption techniques, a computer program is used to encrypt the data, and the vendor who wrote it knows the ‘encryption key’ and can access the information. In such cases, there is a chance of a security compromise. However, in hardware-based encryption, an electronic chip is used to encrypt the data and generate the key. Thus, nobody can read the encrypted information, enabling top secrecy and security.

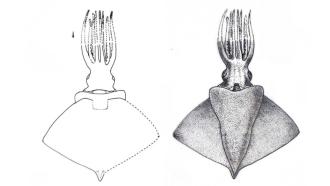

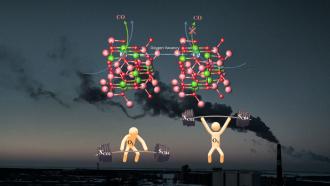

In the new encryption technology developed by Prof. Udayan Ganguly’s group, the researchers generate a unique key, comprising a string of bits, for every electronic chip. The encryption unit of each chip contains an array of tiny capacitors that store electric charge. All the capacitors have an insulator material sandwiched between two metal plates. When a voltage is applied to this collection of capacitors, the insulator layer in some capacitors breaks down randomly.

Each chip has a unique pattern of how the capacitors break down. “It is like your fingerprint. All humans are very alike, but have a unique fingerprint”, explains Prof. Udayan Ganguly. In the chip, the broken capacitors represent a ‘1’ and those that are intact correspond to a ‘0’. This random pattern of ‘0’s and ‘1’s gives a chip its unique identity.

How is this random pattern used for encryption? The device that needs access to the chip asks it a set of questions during the initial setup. It stores the chip’s responses generated based on the random pattern in the encryption unit. For subsequent access, the external device asks a few questions from the set and validates the answers with those stored from the setup. This process is very similar to the security questions that banking websites ask, say the researchers.

The researchers figured out that burning exactly half the number of capacitors gives maximum randomness and ensures the unique identity of each chip. To ensure that only half of the capacitors break down, the researchers used capacitors in pairs and designed a special circuit to ensure that only one of the capacitors in the pair broke down. Besides, since the encryption unit is a part of the chip, it has to be burnt at the average operating voltage to prevent any unintentional damage. The researchers picked the right insulator material and the duration of applying voltage to achieve this.

The researchers tested the new hardware-based encryption scheme in their lab and at SCL. Mr Sunny Sadana, a member of the team, demonstrated the lab results and reproduced them during the manufacturing process. Ashwin Lele, an undergraduate student, developed a method to analyse the performance of the generating the unique pattern for each chip. The researchers also tested the chip at high temperatures to understand how it behaved over time. The results of these tests were satisfactory, say the researchers.

Though the primary purpose of such encryption techniques is in strategic applications like military communication, the research can be applied to broader electronic circuits too. As the encryption is now on the chip, solutions like the Internet of Things (IoT), which involves many sensors and electronic circuits, can also be secured. It can also be used to address the not-yet-widely-discussed issue of secure communication in smart city applications. “Indigenous hardware security capability at the chip manufacturing technology level is critical for national infrastructures like smart cities and strategic interests”, says Dr. S. K. Vasudeva, Scientific Consultant (Defence Technologies) office of Principal Scientific Adviser to Govt of India.

So what would it take to make this technology commercially viable? It would only require a change in the system design, says Prof Udayan Ganguly. “The technological specifications of strategic applications are more stringent than commercial applications. So technology wise, commercial use is possible”, he adds. The researchers have also partnered with the Indian Institute of Technology Delhi and Society for Electronic Transactions and Security, Chennai, to develop products for strategic applications using this technology.