In research to be shared at the prestigious 56th International Reliability Physics Symposium (IRPS), researchers from the Indian Institute of Science Bangalore (IISc) will present a paper that details a breakthrough in significantly improving the reliability limits of 3D FinFET technology in sub-14nm technology for System-on-Chip integration. The study is the result of work in collaboration with Intel that sought to better understand various aspects of electrostatic discharge (ESD), latch-up and hot carrier reliability of ultra-dense FinFET technologies. The team reached a significant milestone in understanding the fundamental knobs dictating various degradation and failure modes. The symposium is held in San Francisco, USA

The research also explores new possibilities of integrating high voltage functionalities in FinFET nodes. Making the FinFET devices to work in a narrow operating window or working at smaller voltages is less challenging than making them work under extended conditions with various reliability threats or operating them at higher voltages, for eventual integration in System on Chips (SoC).

Prof. Mayank Shrivastava, who is leading this effort at IISc Bangalore explained that “For system on chip (SoC) integration, besides low voltage functionalities, you need highly reliable devices capable of handling higher voltage and special ESD protection devices. For instance, the logic, memory and computational blocks in the SoCs can be implemented using sub-1V devices. However one may need 1.8V or 3.3V devices to interface the chips with the external world, which are called Input / Output (I/O) devices. Similarly, one requires 5V or 10V high voltage FinFET devices (often known as LDMOS) to develop power management modules as well as integrated RF power amplifiers. Beside various functional devices, SoC integration requires special ESD protection devices and additional ruggedisation of functional devices.”

Prof. Shrivastava says this achievement of enhancing reliability limits of ultra-dense FinFETs and inventing special ESD protection and high voltage devices for the same is a breakthrough. Through the research, the electrical engineers were able to explain the mechanisms behind ESD, latch-up and hot carrier reliability in FinFET devices. Weak ESD robustness against exposure to high ESD stress at the end-user side had been a roadblock for the construction of high voltage interfaces and SoC integration in 3D FinFET nodes. The insight into the physics of the various device reliability and high voltage operation now allows the development of highly rugged devices. This is a significant milestone regarding enabling FinFET technology for SoC integration.

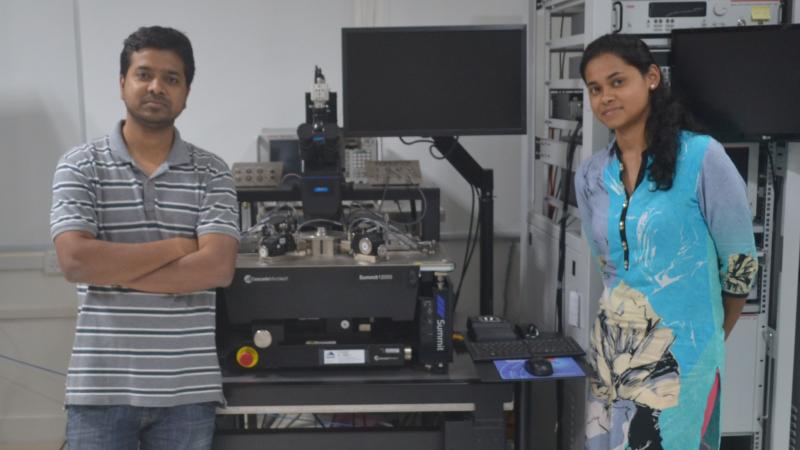

The Ph.D. students supported by Intel under this collaboration at IISc Bangalore, are Milova Paul and B. Sampath Kumar. Dr. Harald Gossner, a senior principal engineer at Intel, was involved in the research activity and called it one of finest examples of academia-industry interaction which has resulted in substantial value addition to the two collaborating partners.

Shrivastava said that this collaboration has been beneficial in exposing students to challenging real-world industry problems, and has provided them with a chance to closely interact with one of the world's largest semiconductor company. "Though we have been interacting with many semiconductor industries, this interaction with Intel is particularly different because of the immense trust Intel had in our capabilities and the information as well as mentorship that they were willing to share. Since the industries in the semiconductor business survive on their intellectual property (IP), it was important for us to realise the value of IP, and we sometimes had to go that extra mile in educating our students specifically on these aspects. We are happy that this interaction between IISc Bangalore & Intel is turning out to be a win-win situation for both the parties involved, which has resulted into several key IPs and series of high-value publications", Prof. Shrivastava stated.

Those interested can hear the presentation by attending the symposium March 11-15 at the San Francisco Airport Hyatt Regency.